-基于Synopsys公司先进的EDA工具

概述

Synopsys(新思科技)公司(Nasdaq: SNPS)是全球领先的电子设计自动化,即EDA软件工具领导厂商。其产品线覆盖SoC设计开发、ASIC设计开发、FPGA开发,并提供丰富的IP库。在售前还可以给客户提供对应的深度定制的解决方案,售后技术支持反映迅速,效率高。并提供多种方式技术支持交互途径

今天的FPGA设计

一方面可编程逻辑器件的价值在于可以通过快速的原型验证使产品的面市时间大大缩短.虽然我们想让产品尽快面市,但同时也要考虑产品的经济性,就需要在器件的性能和价格之间作一个折中.在满足设计功能的情况下,逻辑综合在一个产品的开发过程是及其重要的。因此,选择一个好的逻辑综合解决方案十分关键!

另一方面FPGA器件的逻辑规模及复杂程度越来越大,给验证工程师的工作开展带来很大的难度,首先是仿真器的速度和容量受限,普通仿真器很难完成带有时序信息的后仿真验证;其次是原型验证单板的设计要求越来越高,稳定性和信号完整性尤为重要,这都使产品的发布滞后,所以选择一款高性能的仿真器和现成的高性能的原型验证开发平台至关重要!这就是Synopsys公司成为FPGA逻辑综合及原型验证领域领导者的原因。当然synopsys公司还有其他的辅助工具可以有效的帮助设计工程师和验证工程师严把FPGA设计流程中的每一个环节,确保在规定的时间内完成设计任务。

在世界范围内,越来越多的设计工程师认识到了Synopsys公司FPGA解决方案的优越性。Synopsys的FPGA产品专注于增强高密度和高性能可编程逻辑设计的能力。

完整的FPGA设计解决方案

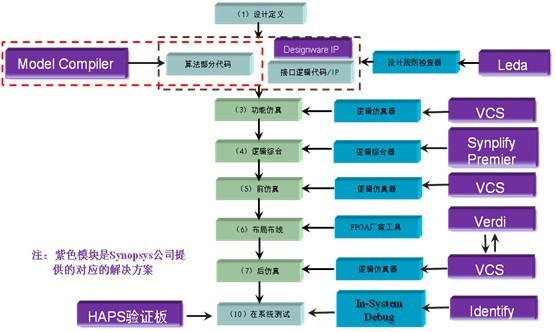

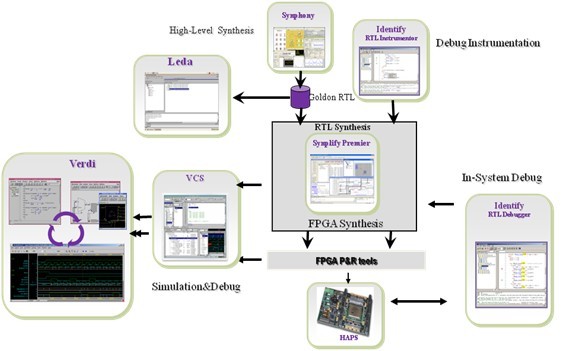

Synopsys公司分别于2008年和2012年先后收购了Synplicity公司、Springsoft公司和EVE等,其中Synplicity的工具涵盖了可编成逻辑器件(FPGAs、PLDs和CPLDs)的综合,验证,调试,物理综合及原型验证等领域;Springsoft公司和EVE为复杂的大规模FPGA设计提供先进的验证解决方案。这些工具被很好的兼容在原有的开发设计平台下,其中最为典型的基于Synopsys先进EDA工具的FPGA设计开发解决方案如图1所示,以后可能会有更多后端验证的工具加入此平台下,可以让验证工程师很轻松的完成验证任务,请多关注我们的网站更新,即将会有更加完善的FPGA设计开发和验证解决方案推出。

图1

解决方案主要部件

1 丰富的IP资源库

DesignWare知识产权

新思科技作为重要的接口和模拟IP 供应商,为SoC 设计提供高质量和经过硅验证的完整解决方案。新思科技拥有广泛的IP 产品,其中包括:

- 全套的接口IP 解决方案,包括控制器、PHY 和业界使用最广泛的验证IP, 如USB、PCI Express、DDR、SATA、HDMI、MIPI 和以太网。

- 模拟IP,包括模拟数字转换器(ADCs)、数字模拟转换器(DACs)、Audio Codecs、Video Analog FrontEnds 和触摸屏模拟前端。

- DesignWare® 单元库包括150 多个用于设计和验证的重要基础IP。

- DesignWare minPower 组件是独特的、经过功耗优化的数据通道结构,可降低移动设备和高性能应用中的动态和泄漏功耗。

- SystemCTM 事务级模型,用于实现快速的投片前基于虚拟平台的软件开发

凭借健壮的IP 设计方法学,为提升质量大量资金投入和全方位的技术支持,新思科技使设计人员能够加速产品上市时间,降低集成风险

2 算法部分RTL代码实现解决方案

高层次DSP算法综合技术

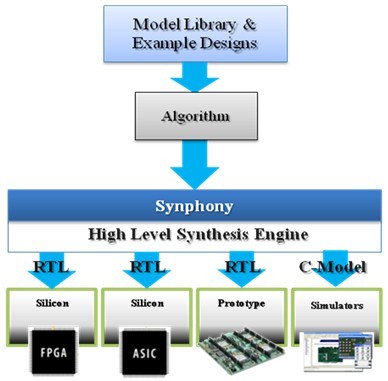

Synphony HLS是一种基于语言和模型的高级综合(HLS)技术,提供一条从算法概念到硅片的高效路径。设计工程师可以使用数学语言和IP模型库(Design Ware IP)构建高级算法模型,然后使用Synphony HLS引擎综合出优化后的ASIC和FPGA的RTL实现,从而进行算法架构探测和快速原型设计,此外,Synphony HLS还能生成高性能的C模型,用于在虚拟平台下进行系统验证和早期软件开发。

Synphony HLS有Model Compiler和C Compiler两款软件。

(1) Synphony Model Compiler的输入是经过验证的Simulink系统模块,通过Synphony Model Compiler,可以自动生成基于系统级优化的RTL源代码,该代码可以直接进行后续的综合,布局布线和调试。

(2) Synphony C Compiler可以生成高性能的C模型,用于在虚拟平台下进行C代码到RTL代码的转换、系统验证和早期软件开发。

3 代码规则检查工具

Synopsys 的 LEDA 是一种可编程代码设计规则检查器,它提供全芯片级混合语言(Verilog 和 VHDL)处理能力,从而加快了复杂设计的开发。LEDA 预装的检查规则大大地增强了设计人员检查 HDL 代码的能力,包括可综合性,可仿真性、可测试性和可重用性。帮助设计师可以在设计的早期发现模型源代码中的隐患与不足,及时的修改和完善源代码,以达到源代码最优化的目的,减少下游工作开展的设计反复次数。

4 高性能的仿真工具

VCS 数字逻辑仿真器和 VCS MX 混合 HDL 语言仿真器都是 Synopsys 的智能 RTL 验证解决方案的基石。VCS 是业界领先的仿真器,支持本征断言(native assertion)描述、自动测试平台生成技术(testbench)、以及代码和断言覆盖引擎,确保智能化验证的实现、设计验证的效率、性能和质量,并缩短了验证周期。

5 先进的自动化侦错工具

Verdi是一款自动侦错工具,通过统一的编译器,读入设计和测试模块,在工具内部产生开放的基于当前设计系统的数据库,同时可以配合VCS做设计的自动化侦错,通过读取VCS仿真产生的VCD波形文件,获得系统行为分析必备的基于事件的系统响应,通过一系列的行为、结构分析引擎,对系统的响应过程进行详细而全面的分析,从而获得了报告系统行为历史和推算系统行为的能力,所以verdi可以通过一系列可视化的模块,如Temoral Flow View、代码调试窗口、电路图察看窗口、波形察看窗口和状态机气泡图,展示系统行为、追踪信号变化的历史过程,进而实现追踪错误信号的目的。

利用Verdi自动化纠错工具,设计工程师和验证工程师在功能验证和时序验证中快速地分离,定位设计问题的源头,从而加速系统设计的进程,确保整个发周期的进度.

6 先进的FPGA综合工具

Synplify_Premier

Synopsys的FPGA产品成为了衡量其它FPGA产品的一个标准,其中Synplify Premier软件的面世,进一步巩固了Synopsys在FPGA综合领域领先的地位。SynplifyPremier不仅继承了明星产品Synplify Pro的全部功能,更加入了众多强大的FPGA综合选项,可以轻松应对复杂的高端FPGA设计和单芯片ASIC 原型验证,可以极大地提高综合效率。

Synplify Premier继承Synplify Pro的全部功能:

- BEST算法对设计进行整体优化

- 自动对关键路径做Retiming,可以提高性能高达25%

- 支持VHDL和Verilog的混合设计输入,并支持网表*.edn文件的输入

- 增强了对System Verilog的支持

- Pipeline功能提高了乘法器和ROM的性能

- 有限状态机优化器可以自动找到最优的编码方法

- 在timing报告和RTL视图及RTL源代码之间进行交互索引

自动识别RAM,避免了繁复的RAM例化

Synplify Premier的创新功能:

- 引入Graph-Based物理综合选项,提供一键式物理综合流程,有效提升芯片时序表现

- 整合功能强大的R T L 调试工具( Identify RTL Debugger),综合调试一气呵成

- 支持Gated Clock及DesignWare组件的转换,便于使用单颗FPGA进行原型验证

7 超高性能、超大规模的原型验证硬件平台

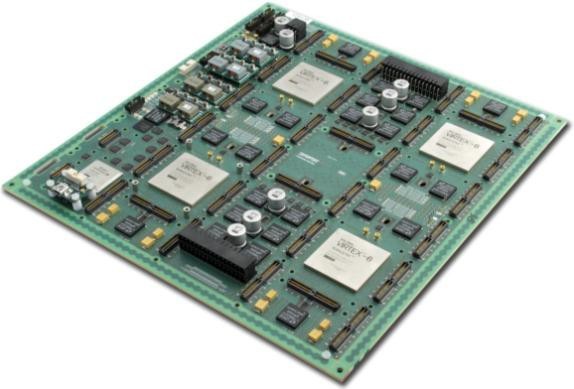

HAPS系列验证板是Synopsys针对于复杂的、大规模的FPGA/ASIC设计,推出的一款高性能大规模的原型验证硬件平台。以HAPS-64母板为例,板载4颗Xilinx V6FPGA芯片,总规模可以达到1800万逻辑门。

HAPS系列验证板可以做到:

- 以接近实时的速度验证和调试软件和硬件

- 在做FPGA/ASIC综合和布局布线之前验证产品的功能,节约数月的开发时间

- 实现软件和硬件的协同测试,在测试芯片功能的同时测试软件的功能

- 验证硬件设计要比仿真器快100 倍以上

- 在产品开发出来之前,使用HAPS 可以提前为客户demo 芯片和产品的功能

7 可视化的调试工具

Synopsys 的Identify 工具允许FPGA 设计者以一种类似于RTL 仿真器的方式对硬件进行调试。其中Identify包括Identify Instrumentation 和 Identify Debugger两个组件,首先设计工程师或验证工程师可以借助Identify Instrumentation在RTL 源码中直接控制硬件的触发点,设置完成之后经过综合和布局布线之后下载到HAPS系列验证板或是目标板(含JTAG接口),上板加电调试可以借助Identify Debugger在源码中直接看到采集上来的数据或是查看波形文件。这种便利使得定位复杂功能问题的时间大大的缩短,常常可以将本来所需的几周到几个月的时间,缩短到只有几天。

补充说明

在以后的FPGA设计开发流程中,可能为了适应更大规模的设计,将会在标准的FPGA设计流程中增加更加先进的后端验证工具,其中包括用于静态时序检查的Primetime和用于等效性检查的Formality等,这两款工具都是采用静态的验证手段,在后端验证过程中,不需要加入测试激励即可完成对网表的时序分析和功能一致性分析,确保网表的时序收敛和功能的正确性;由于是采用静态验证手段,因此验证周期将会大大缩短。

售后服务支持体系

新思科技中国具备完善可靠和响应及时的售后服务体系,这包括

- · 售后服务

新思科技中国的技术支持中心提供了功能强大的基于互联网的技术支持平台SolvNet,通过SolvNet,用户可以通过关键字检索到SolvNet 知识库,包括产品手册,应用指南(Application Notes),技术白皮书(White Papers),版本更新信息(Release Notes)以及大量解决实际技术问题的SolvNet 文章。用户可以通过SolvNet 提交技术问题,并全程跟踪问题解决的过程。这是用户的技术问题到达 Synopsys 产品应用工程师手中最快捷的途径。Synopsys 技术支持中心推荐用户在网络条件允许的情况下尽量使用SolvNet。关于 SolvNet 的注册和使用入门,请参照:SolvNet 的注册和使用。注册用户可以通过电子邮件将技术问题发送到Synopsys 技术支持中心。邮件信箱为prchelp@synopsys.com。技术支持中心值班工程师将定时分拣信箱中的邮件,将它转给专门负责该产品的应用工程师。

注册用户也可以在工作时间(9:00AM-6:00PM)拨打免费电话400-670-7677 获得技术支持。值班工程师将记录下用户的问题及联系方式。随后相关的产品应用工程师将尽快回复用户。